# M63532P

## 32Kx32 PIPE-LINED BRAM LOW VOLTAGE CACHE BURST SRAM

#### PRELIMINARY DATA

- 32Kx32 SYNCHRONOUS SRAM

- LOW VOLTAGE: 3.3V ± 0.3V

- PIPE-LINED OUTPUT REGISTERS SUPPORTS 3-1-1-1 CACHE BURST LINE FILLS

- FAST CYCLE TIMES: 75, 66, 60MHz

- CLK to DATA ACCESS: 7, 8, 9ns Max

- INTERLEAVE or LINEAR BURST COUNTER

- INPUT & OUTPUT REGISTERS

- SELF-TIMED WRITE CYCLE

- THREE STATE COMMON I/O

- ASYNCHRONOUS OUTPUT ENABLE (OE)

- BURST CONTROL INPUTS: ADSP, ADSC, ADV

- BYTE WRITE SELECTS: (BWE1 BWE4)

- GLOBALWRITE ENABLE (GW)

- JEDEC STANDARD 100 PIN TQFP

- SNOOZE MODE INPUT

#### DESCRIPTION

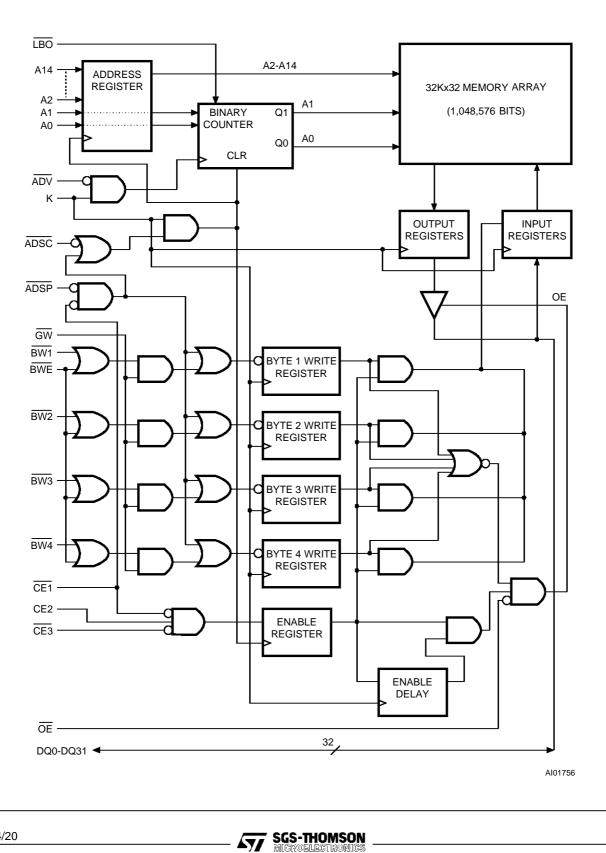

The M63532P BRAM<sup>®</sup> is a 1,048,576-bit CMOS Burst SRAM, organized as 32,768 words x 32 bits. It is fabricated using SGS-THOMSON's low power, high performance, 3.3V HCMOS technology. The device integrates a 2-bit burst counter, address registers, input and output registers, and high speed synchronous SRAM onto a single chip. The M63532P is specifically adapted to provide a burstable, high performance secondary cache for fourth and fifth generation X86 and RISC microprocessors. The device has output registers to support pipe-lined read operations where output data is provided from the previous cycle at the rising edge of clock.

The M63532P is available in a 100 pin 14x20mm JEDEC standard thin quad plastic flat-pak (TQFP). The device provides multiple power and ground pins to reduce effects induced by output noise for high performance applications. All power (V<sub>CC</sub> and V<sub>CCQ</sub>) and ground (GND, and GND<sub>Q</sub>) pins must be used for proper device operation. The BRAM requires a 3.3V $\pm$  0.3V power supply, and all inputs and outputs are TTL compatible.

#### Table 1. Signal Names

| A0-A14           | Address Inputs            |

|------------------|---------------------------|

| DQ0-DQ31         | Data Input/Output         |

| к                | Clock                     |

| LBO              | Linear Burst Order Select |

| BWE              | Byte Write Enable         |

| BW1-BW4          | Byte Write Selects        |

| GW               | Global Write Enable       |

| ŌĒ               | Output Enable             |

| CE1              | Master Chip Enable        |

| CE2              | Active High Chip Select   |

| CE3              | Active Low Chip Select    |

| ADSP             | Address Status Processor  |

| ADSC             | Address Status Controller |

| ADV              | Burst Address Advance     |

| ZZ               | Snooze Mode Input         |

| V <sub>CC</sub>  | Supply Voltage (Core)     |

| GND              | Ground (Core)             |

| V <sub>CCQ</sub> | Supply Voltage (DQ)       |

| GNDQ             | Ground (DQ)               |

|                  |                           |

**Note:** All power and ground pins must be connected for proper device operation.

#### April 1996

This is preliminary information on a new product now in development or undergoing evaluation. Details are subject to change without notice.

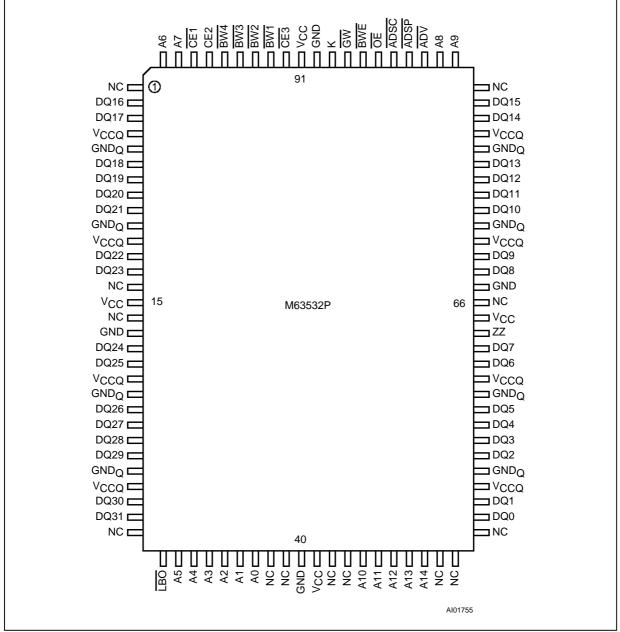

#### **Figure 1. Pin Connections**

Warning: NC = Not Connected.

#### **DEVICE OPERATIONS**

Burst operations can be initiated with either ADSP (processor address status) or ADSC (controller address status). The burst advance input ADV, allows the next burst address to be generated internal to the BRAM.

Cache burst read cycles are initiated with ADSP, without regard to ADSC or BWE, using the external address clocked into the on-chip address registers

when  $\overline{\text{ADSP}}$  is sampled LOW. All Chip Selects must be asserted for  $\overline{\text{ADSP}}$  to begin the burst cycle. The output buffers will be enabled by  $\overline{\text{OE}}$  when the BRAM is selected. If the device is going from a deselect to a select mode, the device will be selected and the outputs enabled on the following clock cycle. In a read operation, data accessed by the current registered address will be available t<sub>KQ</sub> from the next rising clock edge in a pipe-lined fashion.

#### Table 2. Pin Description

| Signal           | I/O    | Property<br>Asserted | Pin#   | Description                                                                                                                                                                                                                      |

|------------------|--------|----------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| К                | I      | CLOCK                | 89     | Clock: All inputs except $\overline{OE}$ and ZZ are synchronous to the rising edge of K.                                                                                                                                         |

| A0-A14           | I      | SYNC                 | Note 1 | Address: Sampled when Chip Selects are true and ADSP or ADSC is asserted active LOW at the rising edge of K.                                                                                                                     |

| DQ0-DQ31         | I/O    | SYNC                 | Note 2 | SRAM data Input/Outputs: DQs remain high impedance except when OE is asserted LOW. Data In is valid during write cycles, Data Out is valid during read cycles provided OE is asserted.                                           |

| CE1              | I      | SYNC, LOW            | 98     | Master Chip Enable: Sampled on the rising edge of K with $\overline{\text{ADSP}}$ or $\overline{\text{ADSC}}$ . When $\overline{\text{CE1}}$ is HIGH, $\overline{\text{ADSP}}$ is blocked. Refer to the synchronous truth table. |

| CE2              | I      | SYNC, HIGH           | 97     | Synchronous Chip Select, used to select the device, and for memory depth expansion. Sampled when a new address is loaded.                                                                                                        |

| CE3              | I      | SYNC, LOW            | 92     | Synchronous Chip Select, used to select the device, and for memory depth expansion. Sampled when a new address is loaded.                                                                                                        |

| ADSP             | I      | SYNC, LOW            | 84     | Address Status Processor: Used to load a new address or select the device.                                                                                                                                                       |

| ADSC             | I      | SYNC, LOW            | 85     | Address Status Cache Controller: Used to load a new address, or select or deselect the device.                                                                                                                                   |

| ADV              | I      | SYNC, LOW            | 83     | Burst Address Advance: Commands internal burst counter.                                                                                                                                                                          |

| GW               | I      | SYNC, LOW            | 88     | Global Write Enable: Supersedes all other write enable inputs.                                                                                                                                                                   |

| BWE              | I      | SYNC, LOW            | 87     | Master Byte Write Enable: Must be asserted with one or more byte select signals during a write cycle to perform a write operation to the SRAM.                                                                                   |

| BW1-BW4          | I      | SYNC, LOW            | Note 3 | Byte Write Selects to select 1 of 8 bit bytes of the 32-bit data bus.                                                                                                                                                            |

| ŌĒ               | I      | ASYNC, LOW           | 86     | Output Enable: Asynchronous DQ control when the device is selected.                                                                                                                                                              |

| LBO              | 1      | STATIC               | 31     | Linear Burst Order: GND = Linear burst count. $V_{CC}$ = Interleave burst count. The LBO input must be tied to $V_{CC}$ or GND, and cannot change during device operation.                                                       |

| ZZ               | I      | ASYNC, HIGH          | 64     | Snooze Mode Input: Overrides all control logic. Requires all inputs at CMOS levels. Asserted HIGH. The ZZ pin is tied to GND if this mode is not used. (See ZZ Mode table and timing.)                                           |

| Vcc              | Supply | 3.3V                 | Note 4 | Core Power Supply: $3.3V \pm 0.3$                                                                                                                                                                                                |

| GND              | Supply | Ground               | Note 5 | Device ground: 0 volts.                                                                                                                                                                                                          |

| V <sub>CCQ</sub> | Supply | 3.3V                 | Note 6 | Isolated Output Buffer Supply: $3.3V \pm 0.3$                                                                                                                                                                                    |

| GNDQ             | Supply | Ground               | Note 7 | Isolated Output Buffer Ground: 0 volts.                                                                                                                                                                                          |

Notes: 1. Address inputs are listed respectively as A0-A14: 37,36,35,34,33,32,100,9982,81,44,45,46,47,48. 2. DQs are listed respectively as D0-D31: 52,53,56,57,58,5962,63,68,69,72,73,74,75,78,79,2,3,6,7,8,9,12,13,18,19,2223,24,

25,28,29.

25,28,29.

3. Byte Write Selects are listed respectively as: BW1, BW2, BW3, BW4: 93,94,95,96

4. V<sub>CC</sub> pins: 15,41,65,91

5. GND pins: 17,40,67,90

6. V<sub>CCQ</sub> pins: 4,11,20,27,54,61,70,77

7. GND<sub>Q</sub> pins: 5,10,21,26,55,60,7176

#### Figure 2. Block Diagram

4/20

| No. | CE1 | CE3 | CE2 | ADSP | ADSC | ADV | WE | OE | к | DQ   | Address  | Operation                     |  |

|-----|-----|-----|-----|------|------|-----|----|----|---|------|----------|-------------------------------|--|

| 1   | н   | х   | х   | х    | L    | Х   | х  | х  | Ŷ | Hi-Z | None     | Deselect,<br>Power-down       |  |

| 2   | L   | Х   | L   | L    | х    | Х   | х  | х  | Ŷ | Hi-Z | None     | Deselect,<br>Power-down       |  |

| 3   | L   | Н   | Х   | L    | х    | Х   | х  | х  | Ŷ | Hi-Z | None     | Deselect,<br>Power-down       |  |

| 4   | L   | Х   | L   | н    | L    | Х   | х  | х  | Ŷ | Hi-Z | None     | Deselect,<br>Power-down       |  |

| 5   | L   | Н   | Х   | н    | L    | Х   | х  | х  | Ŷ | Hi-Z | None     | Deselect,<br>Power-down       |  |

| 6   | L   | L   | н   | L    | х    | Х   | х  | L  | Ŷ | Q    | External | Read Cycle<br>Begin Burst     |  |

| 7   | L   | L   | Н   | L    | х    | Х   | х  | н  | Ŷ | Hi-Z | External | Read Cycle<br>Begin Burst     |  |

| 8   | L   | L   | Н   | н    | L    | Х   | L  | х  | Ŷ | D    | External | Write Cycle<br>Begin Burst    |  |

| 9   | L   | L   | н   | Н    | L    | Х   | н  | L  | Ŷ | Q    | External | Read Cycle<br>Begin Burst     |  |

| 10  | L   | L   | н   | н    | L    | Х   | н  | н  | Ŷ | Hi-Z | External | Read Cycle<br>Begin Burst     |  |

| 11  | x   | Х   | Х   | н    | Н    | L   | н  | L  | Ŷ | Q    | Next     | Read Cycle<br>Continue Burst  |  |

| 12  | х   | х   | Х   | н    | Н    | L   | н  | н  | Ŷ | Hi-Z | Next     | Read Cycle<br>Continue Burst  |  |

| 13  | н   | Х   | Х   | х    | Н    | L   | н  | L  | Ŷ | Q    | Next     | Read Cycle<br>Continue Burst  |  |

| 14  | н   | Х   | Х   | х    | Н    | L   | н  | н  | Ŷ | Hi-Z | Next     | Read Cycle<br>Continue Burst  |  |

| 15  | х   | Х   | Х   | н    | Н    | L   | L  | Х  | Ŷ | D    | Next     | Write Cycle<br>Continue Burst |  |

| 16  | н   | Х   | Х   | х    | Н    | L   | L  | х  | Ŷ | D    | Next     | Write Cycle<br>Continue Burst |  |

| 17  | х   | Х   | Х   | Н    | Н    | Н   | н  | L  | Ŷ | Q    | Current  | Read Cycle<br>Suspend Burst   |  |

| 18  | х   | Х   | Х   | Н    | Н    | Н   | н  | н  | Ŷ | Hi-Z | Current  | Read Cycle<br>Suspend Burst   |  |

| 19  | н   | Х   | Х   | Х    | Н    | Н   | н  | L  | Ŷ | Q    | Current  | Read Cycle<br>Suspend Burst   |  |

| 20  | н   | х   | х   | Х    | Н    | Н   | н  | н  | Ŷ | Hi-Z | Current  | Read Cycle<br>Suspend Burst   |  |

| 21  | х   | Х   | Х   | Н    | Н    | Н   | L  | х  | Ŷ | D    | Current  | Write Cycle<br>Suspend Burst  |  |

| 22  | н   | х   | х   | х    | Н    | Н   | L  | х  | Ŷ | D    | Current  | Write Cycle<br>Suspend Burst  |  |

Table 3. Synchronous Truth Table

Notes: 1. X = Don't Care. H is logic HIGH. L is logic LOW. The ZZ input is presumed LOW for all cases of the truth table.

2. This is a synchronous device. All inputs except OE must meet the specified setup and hold times relative to the rising edge of K.

3. ADSP = LOW at the rising edge of K initiates an internal Read operation when the device selected. (ADSP can be blocked if CE1 is HIGH). A Write operation can only be performed on the subsequent clock.

4. WE = L means a valid write cycle is initiated by proper assertion of write enable signals. AWrite cycle is defined by at least one Byte Write (BW4-BW1) asserted with BWE, and ADSP HIGH for the specified set-up and hold times.

5. READ cycles are defined by all Write Enables held HIGH for the specified set-up and hold times relative to the rising edge of K.

6. For a Write operation following a Read operation, OE must be HIGH to<sub>CHZ</sub> before the input data required setup time and held HIGH throughout the input data hold time.

7. This device contains circuitry that ensures the DOs will be High-Z during power-up.

This device contains circuitry that ensures the DQs will be High-Z during power-up. 8. OE controls the state of the data bus (DQ) when the device is selected. DQs are High-Z when the device is deselected. OE is a

"don't care" when a byte write enable is sampled low initiating a valid Write cycle.

9. The device is presumed selected in a previous cycle for logic states 11-22.

| ZZ               | CE1   | CE3   | CE2   | ADSP  | ADSC  | ADV   | GW    | OE    | к     | DQ    | Address | Operation                               |

|------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------|-----------------------------------------|

| H <sup>(1)</sup> | Х     | Х     | Х     | Х     | Х     | Х     | Х     | Х     | Х     | Х     | Х       | Sleep Mode                              |

| L                | Valid   | See Synchronous<br>Table <sup>(2)</sup> |

#### Table 4. ZZ Mode Truth Table

Notes: 1. When ZZ is asserted HIGH, the device will enter a Snooze Mode within tzzs. K must continue for a minimum of two valid cycles once ZZ goes HIGH.

2. Refer to the Synchronous Truth Table given above.

#### Table 5. Partial Write Truth Table

| Operation       | GW | BWE | BW1 | BW2 | BW3 | BW4 | DQ Control |

|-----------------|----|-----|-----|-----|-----|-----|------------|

| Read            | н  | н   | Х   | Х   | Х   | Х   | Q0-Q31     |

| Read            | н  | L   | н   | н   | Н   | н   | Q0-Q31     |

| Write Byte1     | н  | L   | L   | н   | Н   | н   | D0-D7      |

| Write Byte2     | н  | L   | н   | L   | Н   | н   | D8-D15     |

| Write Byte3     | н  | L   | н   | н   | L   | н   | D16-D23    |

| Write Byte4     | н  | L   | н   | н   | н   | L   | D24-D31    |

| Write All Bytes | н  | L   | L   | L   | L   | L   | D0-D31     |

| Write All Bytes | L  | Х   | Х   | Х   | Х   | Х   | D0-D31     |

Notes: 1. X = Don't Care. H is logic HIGH. L is logic LOW.

2. All byte write signals are synchronous inputs to the rising edge (LOW-to-HIGH) transition of K.

#### DEVICE OPERATIONS (cont'd)

The  $\overline{\text{ADV}}$  input is ignored on the clock edge that samples  $\overline{\text{ADSx}}$  asserted, but is sampled on all subsequent clock edges. The address is incremented internally to the BRAM for each read burst access where  $\overline{\text{BWE}}$  and  $\overline{\text{GW}}$  are sampled HIGH,  $\overline{\text{ADV}}$  is asserted LOW, and both address strobes are HIGH. Data is always valid at t<sub>KQ</sub> for all Outputs (DQ0-DQ31) from the rising of clock (K).

The ADV input (burst address advance) provides control of the burst counter. The ADV input controls subsequent burst data accesses after the first data of the burst cycle is processed. Each time ADV is active low for subsequent bursts at the rising edge of the clock input, the burst counter is advanced to the next burst address. The address is advanced before the operation. The BRAM will suspend the address burst sequence when the ADV pin is high during positive clock transitions. Upon completion of the full internal burst count, the address will wrap-around to its initial base address. The logic state of the LBO input determines the burst sequence as interleave (i486<sup>TM</sup> or Pentium<sup>TM</sup> for Intel bursts) or linear for other processors (RISC, Power PC, Cyrix 6x86).

Write cycles are performed by disabling the outputs with OE prior to asserting BWE.

A global write enable ( $\overline{GW} = LOW$ ) writes all 32 bits regardless of the state of  $\overline{BWE}$  or individual byte write select inputs. When  $\overline{GW}$  is HIGH, one or more bytes can be written by asserting  $\overline{BWE}$  and individual byte write selects ( $\overline{BWE1} - \overline{BWE4}$ ). The byte write table shows which byte write selects controls DQ0-DQ31.  $\overline{BWE}$  is ignored on rising clock edges that sample  $\overline{ADSP}$  LOW, but is sampled on all subsequent rising clock edges.

Output buffers are disabled  $t_{KQHZ}$  after K when BWE or GW is sampled LOW (independent of OE). Data is clocked into the data input register when a proper write operation is implemented. The write cycles are internally self-timed, and are initiated by the rising edge of the clock input. A write burst cycle continues with the address incremented internal to the BRAM when BWE and ADV are sampled LOW at the next rising clock edge.

## Table 6. Asynchronous Truth Table

| Operation                 | ŌĒ | DQ Status        |

|---------------------------|----|------------------|

| Read                      | L  | Data Out         |

| Read                      | Н  | High-Z           |

| Write <sup>(2)</sup>      | Х  | Data In (High-Z) |

| Deselected <sup>(3)</sup> | Х  | High-Z           |

Notes: 1. X = Don't Care. H is logic HIGH. L is logic LOW.

For a cache write cycle following a read operation, OE must be high t<sub>OEHZ</sub> before the input data required set-up time, and be held high through the input data hold time.

3. Deselect from previous cycle.

## Table 7. Interleave Burst Sequence (LBO = $V_{CC}$ )

| Burst Starting Addr          | Begin 1 |   | Begin 2 |    | Begin 3 |    | Begin 4 |    |    |

|------------------------------|---------|---|---------|----|---------|----|---------|----|----|

| Burst Starting Address       |         |   | A0      | A1 | A0      | A1 | A0      | A1 | A0 |

| Load External Address        | A14-A2  | 0 | 0       | 0  | 1       | 1  | 0       | 1  | 1  |

| 1st Burst Address (Internal) | A14-A2  | 0 | 1       | 0  | 0       | 1  | 1       | 1  | 0  |

| 2nd Burst Address (Internal) | A14-A2  | 1 | 0       | 1  | 1       | 0  | 0       | 0  | 1  |

| 3rd Burst Address (Internal) | A14-A2  | 1 | 1       | 1  | 0       | 0  | 1       | 0  | 0  |

Note: The burst count sequence wraps around to the initial address after a full count is completed.

## Table 8. Linear Burst Sequence (LBO = GND)

| Burst Starting Addr          | Begin 1 |   | Begin 2 |    | Begin 3 |    | Begin 4 |    |    |

|------------------------------|---------|---|---------|----|---------|----|---------|----|----|

|                              |         |   | A0      | A1 | A0      | A1 | A0      | A1 | A0 |

| Load External Address        | A14-A2  | 0 | 0       | 0  | 1       | 1  | 0       | 1  | 1  |

| 1st Burst Address (Internal) | A14-A2  | 0 | 1       | 1  | 0       | 1  | 1       | 0  | 0  |

| 2nd Burst Address (Internal) | A14-A2  | 1 | 0       | 1  | 1       | 0  | 0       | 0  | 1  |

| 3rd Burst Address (Internal) | A14-A2  | 1 | 1       | 0  | 0       | 0  | 1       | 1  | 0  |

Note: The burst count sequence wraps around to the initial address after a full count is completed.

<u>Read</u> or Write operations can be initiated with ADSC instead of ADSP. The differences of these inputs are noted as:

1. ADSP must be HIGH when ADSC is asserted LOW to initiate a cycle with ADSC.

2.All Write Enable signals are sampled on the positive going clock edge that samples ADSC LOW (with ADSP HIGH).

3. ADSP is blocked when CE1 is HIGH. The M63532P can be selected with either ADSP or ADSC, but can only be deselected with ADSC when CE1 is HIGH.

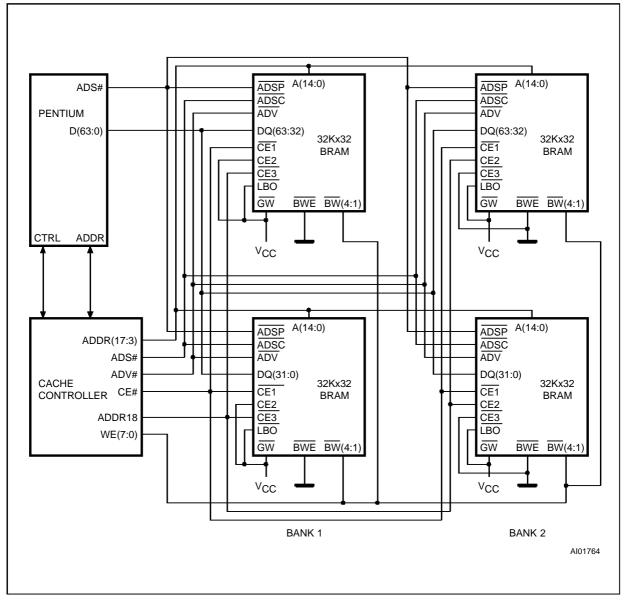

#### **GENERAL APPLICATION**

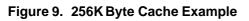

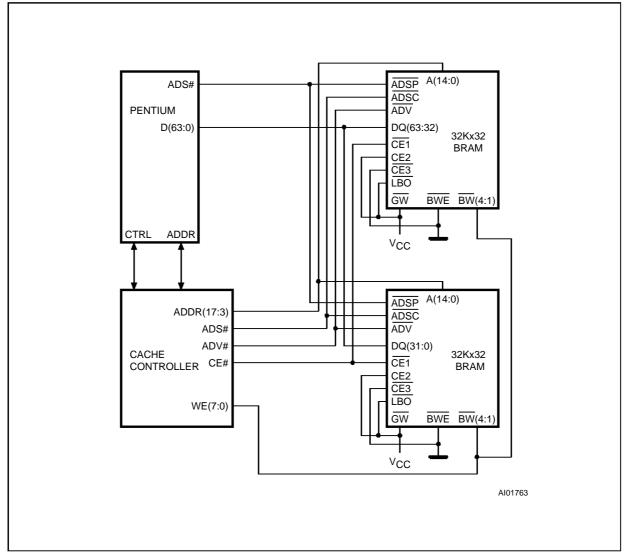

The M63532P provides an architecture for building a 32Kx64-bit burstable L2 data cache SRAM array (256K bytes) by using only two (2) devices. Four(4) devices are needed to provide a 512K byte cache (see Figure 9 and Figure 10). The M63532P BRAM has three chip enables for easy depth expansion. The chip enables are registered to allow contention free operation when implementing a 512K byte, dual-bank cache configuration.

| Previous Cycle (x)                                                        | 1)               | Present                                                | Cycle ()          |     | Next Cycle (z) |                                                    |

|---------------------------------------------------------------------------|------------------|--------------------------------------------------------|-------------------|-----|----------------|----------------------------------------------------|

| Operation                                                                 | <b>BWn</b> (4,5) | Operation                                              | CE <sup>(2)</sup> | BWn | OE             | Operation                                          |

| Initiate WRITE cycle for<br>ALL bytes<br>Address = A(x); Data = D(x)      | ALL Low          | Initiate READ cycle,<br>Register A(y),<br>Q=D(x)       | L                 | Н   | L              | READ Q(y) <sup>(3)</sup>                           |

| Initiate WRITE cycle for<br>ALL bytes<br>Address = $A(x)$ ; Data = $D(x)$ | ALL Low          | READ / DESELECT<br>No new cycle<br>Q=D(x)              | Н                 | Н   | L              | No carry over from<br>previous cycle<br>(Deselect) |

| Initiate WRITE cycle for<br>ALL bytes<br>Address = $A(x)$ ; Data = $D(x)$ | ALL Low          | READ / DESELECT<br>No new cycle<br>Q=High-Z            | Н                 | Н   | Н              | No carry over from<br>previous cycle<br>(Deselect) |

| Initiate WRITE cycle, one byte<br>Address = $A(x)$ ; Data = $D(x)$        | One Low          | READ / DESELECT<br>No new cycle<br>Q=D(x) for one byte | Н                 | Н   | L              | No carry over from<br>previous cycle<br>(Deselect) |

#### Table 9. Write Pass-Thru Truth Table

Notes: 1. Previous cycle (x) can be either Burst or Non-burst. 2. CE = L means all Chip Enable inputs are True. CE = H means one or more Chip Enable inputs are False such that the device is deselected.

3. Write data Pass-Thru will occur when a Read cycle at address (y) is preceded by a Write cycle at address (x). Address (y) will be registered as the new address, and data written at address (x) will appear on the outputs (DQ) during the same clock period. The subsequent read cycle (z) will provide data from address (y) to the DQ pins. The OE input will maintain control of the data bus at all times.

4. BWE is LOW when one or more BWn inputs are LOW.

5. GW = LOW also writes all bytes giving identical results.

#### Table 10. Absolute Maximum Ratings

| Symbol           | Parameter                                               | Value                         | Unit |

|------------------|---------------------------------------------------------|-------------------------------|------|

| TA               | Ambient Operating Temperature                           | 0 to 70                       | °C   |

| T <sub>STG</sub> | Storage Temperature                                     | –65 to 150                    | °C   |

| V <sub>IO</sub>  | Voltage on any Pin Relative to Ground <sup>(1, 3)</sup> | –0.5 to V <sub>CC</sub> + 0.5 | V    |

| Vcc              | Supply Voltage <sup>(1, 2)</sup>                        | –0.5 to +4.6                  | V    |

| lo               | Output Current <sup>(4)</sup>                           | 100                           | mA   |

| PD               | Power Dissipation                                       | 2                             | W    |

Notes: 1. This is a stress rating for transient conditions only. Functional operation of the device at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for

extended periods of time mayaffect reliability. 2. Accelerated life tests are performed with  $V_{CC} = 4.2$  at 125°C 3. All pins except the  $V_{CC}$  pin. DC conditions only where  $V_{CC}$  for this parameter refers to the specified operating range of  $V_{CC}$ , where V<sub>CC</sub> max. is 3.6 volts.

4. Output current absolute maximum rating is specified for one output at a time, not to exceed a duration of 1 second.

| Symbol                           | Parameter               | Min  | Тур. | Мах                   | Unit |

|----------------------------------|-------------------------|------|------|-----------------------|------|

| V <sub>CC</sub>                  | Supply Voltage          | 3.0  | 3.3  | 3.6                   | V    |

| GND                              | Supply Voltage          | 0    | 0    | 0                     | V    |

| V <sub>IH</sub> <sup>(3,5)</sup> | Logic '1' Input Voltage | 2.0  | 3.0  | V <sub>CC</sub> + 0.3 | V    |

| V <sub>IHK</sub> <sup>(3)</sup>  | Logic '1' Clock only    | 2.0  | 3.0  | 5.5                   | V    |

| VIHZZ <sup>(3)</sup>             | Logic '1' ZZ Input      | 2.4  | 3.0  | Vcc + 0.3             | V    |

| V <sub>IL</sub> <sup>(4,5)</sup> | Logic '0' All Inputs    | -0.3 | 0.2  | 0.8                   | V    |

| Vccq                             | Supply Voltage          | Vcc  | 3.3  | Vcc                   | V    |

| GNDQ                             | Supply Voltage          | 0    | 0    | 0                     | V    |

Table 11. Recommended DC Operating Conditions <sup>(1,2)</sup> ( $T_A = 0$  to 70 °C)

Notes: 1. All voltages referenced to GND.

2. Minimum DC input levels are guaranteed at cycle times of 500ns.

3. V<sub>IH</sub> max. = (V<sub>CC</sub> + 1.0) AC (pulse width ≤ tKC/2). Input current limit 200mA.

4. V<sub>IL</sub> min. = -1.0V AC (pulse width ≤ tKC/2). Input current limit 200mA.

5. The LBO pin is a CMOS static input and must be tied to either V<sub>CC</sub> or GND for proper operation.

## Table 12. DC Characteristics (T<sub>A</sub> = 0 to 70 °C, V<sub>CC</sub> = $3.3V \pm 0.3V$ )

| Symbol                         | Parameter                                                                                                                                                                          | Min | Max | Unit |

|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|

| Icca <sup>(1)</sup>            | Average AC Power Supply Current, device selected, ( $\overline{OE}=V_{IH}$ ).<br>All inputs = $V_{IL} = 0.0V$ and $V_{IH} \ge 3.0V$<br>$V_{CC}$ max., K cycle time = $t_{KC}$ min. |     | 290 | mA   |

| I <sub>CC1</sub>               | $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                               |     | 50  | mA   |

| I <sub>SB2</sub>               | TTL Standby Current, device deselected, All inputs are static: $\leq V_{IL}$ or $\geq V_{IH}$ ; $V_{CC}$ max., K cycle time = 0.                                                   |     | 18  | mA   |

| I <sub>SB3</sub>               | CMOS Standby Current, device deselected, All inputs are static:<br>$\leq$ (GND + 0.2) or $\geq$ (V <sub>CC</sub> - 0.2); V <sub>CC</sub> max., K cycle time = 0.                   |     | 5   | mA   |

| I <sub>SB4</sub>               | Device deselected, All inputs are static: $\leq$ (GND + 0.2) or $\geq$ (V <sub>CC</sub> - 0.2); V <sub>CC</sub> max., K cycle time = t <sub>KC</sub> min.                          |     | 50  | mA   |

| I <sub>LI</sub> <sup>(2)</sup> | Input Leakage Current (Any Input)                                                                                                                                                  | -2  | 2   | μA   |

| I <sub>LO</sub> <sup>(2)</sup> | Output Leakage Current                                                                                                                                                             | -2  | 2   | μA   |

| V <sub>OH</sub> <sup>(3)</sup> | Output Logic '1' Voltage (I <sub>OH</sub> = -4.0mA)                                                                                                                                | 2.4 |     | V    |

| V <sub>OL</sub> <sup>(3)</sup> | Output Logic '0' Voltage (I <sub>OL</sub> = 8mA)                                                                                                                                   |     | 0.4 | V    |

Notes: 1. I<sub>CCA</sub> measured as average AC current, with outputs open, V<sub>CC</sub> max., t<sub>KC</sub> (min) cycle 100%. All addresses are registered

every other cycle. 2. Measured with  $GND_Q \le V \le V_{CC}$  and outputs deselected. 3. All voltages referenced to  $GND_Q$ .

| Symbol            | /mbol Parameter                           |   | Мах | Units |

|-------------------|-------------------------------------------|---|-----|-------|

| Cı                | Input Capacitance on all pins (except DQ) | 5 | 7   | pF    |

| Co <sup>(2)</sup> | Output Capacitance (DQ0-DQ31)             | 6 | 8   | pF    |

## Table 13. Capacitance <sup>(1)</sup> ( $T_A = 25^{\circ}C$ , f = 1 MHz)

Notes: 1. Capacitances are sampled and not 100% tested. 2. Output buffers are deselected.

#### Table 14. Termal Consideration

| Symbol          | Description Conditions                     |                                                                          | Тур | Units |

|-----------------|--------------------------------------------|--------------------------------------------------------------------------|-----|-------|

| Θ <sub>JA</sub> | Thermal resistance,<br>Junction to Ambient | Still Air, soldered onto a 4.34 x<br>1.13 inch, 8 layer, Printed Circuit | 31  | °C/ W |

| O JC            | Thermal resistance,<br>Junction to Case    | Board                                                                    | TBD | °C/ W |

## Table 15. AC Test Condition

| Input Levels                                   | GND to 3.0V     |

|------------------------------------------------|-----------------|

| Transition Time                                | 1.5 ns          |

| Input and Output Signal Timing Reference Level | 1.5 Volts       |

| Ambient Temperature                            | 0°C to 70°C     |

| Vcc                                            | $3.3V \pm 0.3V$ |

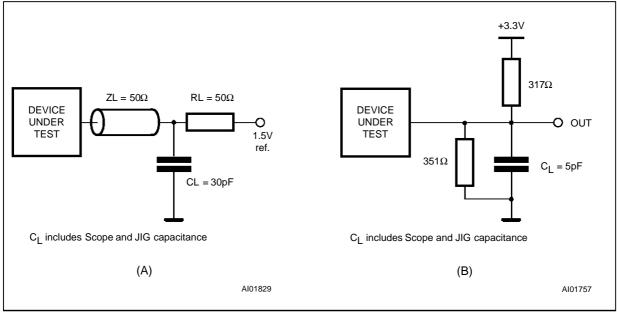

## Figure 3. AC Test Load Circuit<sup>(1)</sup>

Note: 1. Capacitive load consists of test environment.

SGS-THOMSON

10/20

|                                     |                                                     | M63532P |      |      |      |      |      |       |

|-------------------------------------|-----------------------------------------------------|---------|------|------|------|------|------|-------|

| Symbol                              | Parameter                                           | -7      |      | -8   |      | -9   |      | Units |

|                                     |                                                     | Min.    | Max. | Min. | Max. | Min. | Max. |       |

| t <sub>KC</sub>                     | Cycle Time                                          | 13.3    |      | 15   |      | 16.7 |      | ns    |

| t <sub>KQ</sub> <sup>(1)</sup>      | Clock Access Time                                   |         | 7    |      | 8    |      | 9    | ns    |

| $t_{OEQ}$ <sup>(1)</sup>            | Output Enable Access Time                           |         | 5    |      | 6    |      | 6    | ns    |

| tkqlz <sup>(2, 5)</sup>             | Clock High to Q Active (Low-Z)                      | 2       |      | 2    |      | 2    |      | ns    |

| t <sub>KQX</sub> <sup>(1)</sup>     | Clock High to Q Change                              | 2       |      | 2    |      | 2    |      | ns    |

| t <sub>OELZ</sub> (2, 5)            | Output Enable to Output Active                      | 0       |      | 0    |      | 0    |      | ns    |

| t <sub>KQHZ</sub> <sup>(2, 5)</sup> | Clock High to Q High-Z                              |         | 5    |      | 6    |      | 6    | ns    |

| t <sub>OEHZ</sub> <sup>(2, 5)</sup> | Output Disable to Q High-Z                          |         | 5    |      | 6    |      | 6    | ns    |

| t <sub>KH</sub> <sup>(3)</sup>      | Clock High Pulse Width                              | 4.5     |      | 5.5  |      | 6    |      | ns    |

| t <sub>KL</sub> <sup>(3)</sup>      | Clock Low Pulse Width                               | 4.5     |      | 5.5  |      | 6    |      | ns    |

| t <sub>AS</sub> <sup>(4)</sup>      | Address Set-up Time                                 | 2.5     |      | 2.5  |      | 2.5  |      | ns    |

| t <sub>ADSS</sub> (4)               | Address Status Set-up Time                          | 2.5     |      | 2.5  |      | 2.5  |      | ns    |

| t <sub>DS</sub> <sup>(4)</sup>      | Data In Set-up Time                                 | 2.5     |      | 2.5  |      | 2.5  |      | ns    |

| t <sub>WS</sub> <sup>(4)</sup>      | Write/ Read Set-up Time                             | 2.5     |      | 2.5  |      | 2.5  |      | ns    |

| t <sub>AAS</sub> <sup>(4)</sup>     | Address Advance Set-up Time                         | 2.5     |      | 2.5  |      | 2.5  |      | ns    |

| t <sub>CES</sub> <sup>(4)</sup>     | Chip Enable Valid Set-up Time                       | 2.5     |      | 2.5  |      | 2.5  |      | ns    |

| t <sub>AH</sub> <sup>(4)</sup>      | Address Hold Time                                   | 0.5     |      | 0.5  |      | 0.5  |      | ns    |

| t <sub>ADSH</sub> <sup>(4)</sup>    | Address Status Hold Time                            | 0.5     |      | 0.5  |      | 0.5  |      | ns    |

| t <sub>DH</sub> <sup>(4)</sup>      | Data In Hold Time                                   | 0.5     |      | 0.5  |      | 0.5  |      | ns    |

| t <sub>WH</sub> <sup>(4)</sup>      | Write / Read Hold Time                              | 0.5     |      | 0.5  |      | 0.5  |      | ns    |

| t <sub>AAH</sub> <sup>(4)</sup>     | Address Advance Hold Time                           | 0.5     |      | 0.5  |      | 0.5  |      | ns    |

| t <sub>CEH</sub> <sup>(4)</sup>     | Chip Enable Hold Time                               | 0.5     |      | 0.5  |      | 0.5  |      | ns    |

| t <sub>CFG</sub> <sup>(6)</sup>     | Configuration Set-up Time Prior to Device Operation | 50      |      | 50   |      | 50   |      | ns    |

## Table 16. Read/Write AC Characteristics (T<sub>A</sub> = 0 to 70 °C, V<sub>CC</sub> = $3.3V \pm 0.3V$ )

Notes: 1. Measured with load as shown in Figure 3A.

2. Transition is measured ± 200mV from steady-state voltage with load as shown in Figure 3B. This parameter is sampled and not 100% tested.

3. This parameter is characterized and guaranteed and not 100% tested.

4. This is a synchronous device requiring that all inputs must meet the specified set-up and hold times with stable logic levels for all rising edges of the clock input (K).

5. At energing reporting the parameter is parameter in logo than target.

At any given temperature or voltage condition, t<sub>KHQZ</sub> is less than t<sub>KQLZ</sub>, and t<sub>OEHZ</sub> is less than t<sub>OELZ</sub>.

Configuration signal LBO is static and must not change during normal operation.

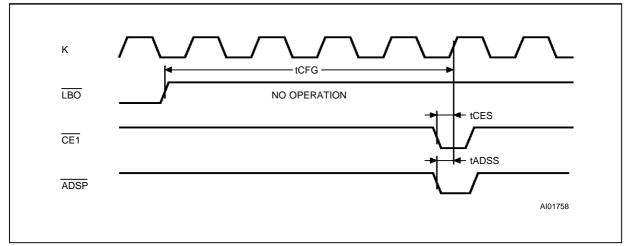

#### Figure 4. Configuration Timing

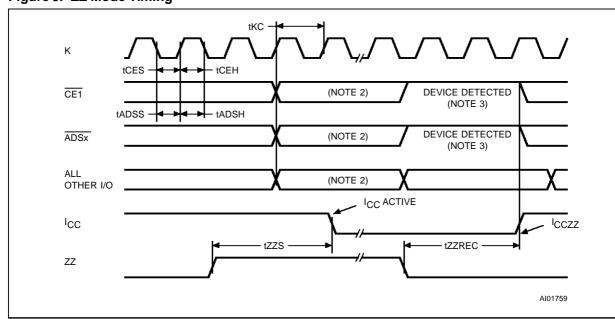

## Figure 5. ZZ Mode Timing

## Table 17. ZZ Mode Data Retention Characteristics<sup>(1)</sup>

(T<sub>A</sub> = 0 to 70 °C, V<sub>CC</sub> =  $3.3V \pm 0.3V$ )

| Symbol                            | Description                           | Conditions                                                                                                                                        | Min              | Мах              | Unit |

|-----------------------------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|------|

| Icczz <sup>(2)</sup>              | ZZ Mode Current                       | $V_{\text{IN}} \geq (\text{Vcc}-0.2\text{V}) \text{ or } \leq 0.2\text{V}; \ \ \text{V}_{\text{CC}} = 3.3\text{V}$                                |                  | 2000             | μA   |

| tzzs <sup>(2)</sup>               | Device Operation to ZZ<br>StandbyTime | $\begin{array}{l} ZZ = HIGH \\ V_{IN} \geq (V_{CC} \text{ - } 0.2 \text{V}) \text{ or } \leq 0.2 \text{V}; \ \ V_{CC} = 3.3 \text{V} \end{array}$ |                  | 2t <sub>KC</sub> | ns   |

| t <sub>ZZREC</sub> <sup>(3)</sup> | ZZ Recovery Time                      | ZZ = LOW                                                                                                                                          | 2t <sub>KC</sub> |                  | ns   |

Notes: 1. The ZZ input pin is an asynchronous input asserted active HIGH. Any access pending when entering Snooze Mode is not considered valid, and completion of the operation is not guaranteed. Snooze Mode must not be initiated during a pending operation. It is suggested that the device be deselected before entering the Snooze Mode.

2. The assertion of ZZ allows the SRAM to enter a low power standby mode. Data integrity is guaranteed. All pins including the ZZ input =  $V_{IN} \ge (V_{CC} - 0.2V)$  or (GND ± 0.2V).

3. Chip Enables must remain False for the duration of tzzREC after the ZZ input returns LOW. Both ADSP and ADSC must remain HIGH during tzzREC.

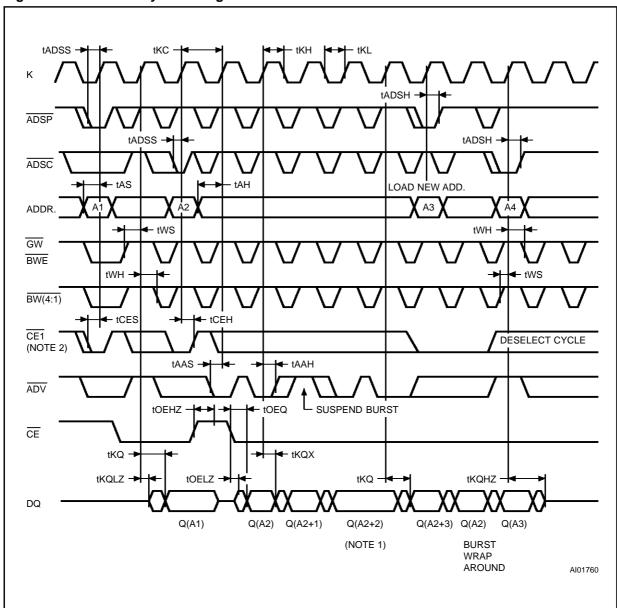

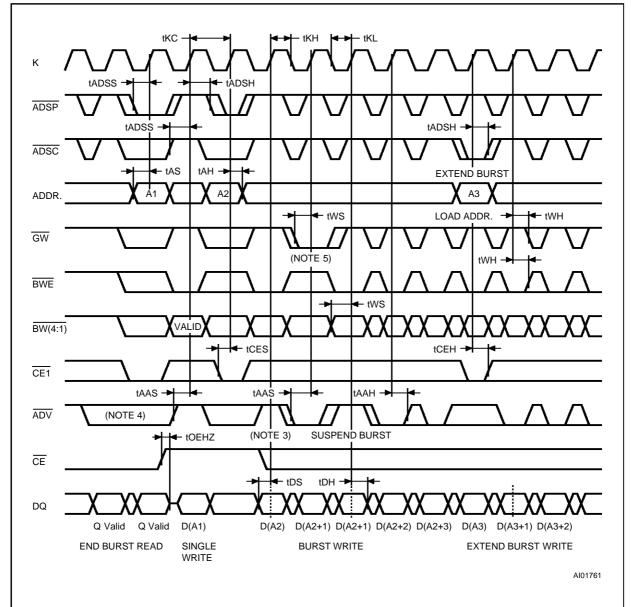

#### Figure 6. Burst Read Cycle Timing <sup>(3)</sup>

Notes: 1. Q (A2) represents the first output data from the base address A2. Q (A2+1) is the next output data in the burst read sequence with A2 as the base address. This is followed by subsequent bursts of output data Q(A2+2) and Q(A2+3) from base address A2.

2. In this diagram all Chip Enables have identical timing to CE1. CE1 and CE3 are LOW while CE2 is HIGH. CE1 and CE3 are

HIGH while CE2 is LOW.

3. This diagram shows the device as deselected at the beginning the timing sequence.

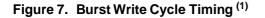

Notes: 1. D (A2) represents the first input data for the base address A2. D (A2+1) is the next input data in the burst write sequence with A2 as the base address. This is followed by subsequent bursts of input data D(A2+2) and D(A2+3) from base address A2.

2. In this diagram all Chip Enables have identical timing to CE1. CE1 and CE3 are LOW while CE2 is HIGH. CE1 and CE3 are

HIGH while CE2 is LOW.

3. ADV must be HIGH to permit a Write operation to the loaded address when using ADSP to load the external address.

OE must beHIGH prior to the input data set-up and held HIGH at least tDH. This prevents data bus contention.

All bytes are written when GW is sampled LOW ,or GW is HIGH and BWE=BW1-BW4=LOW.

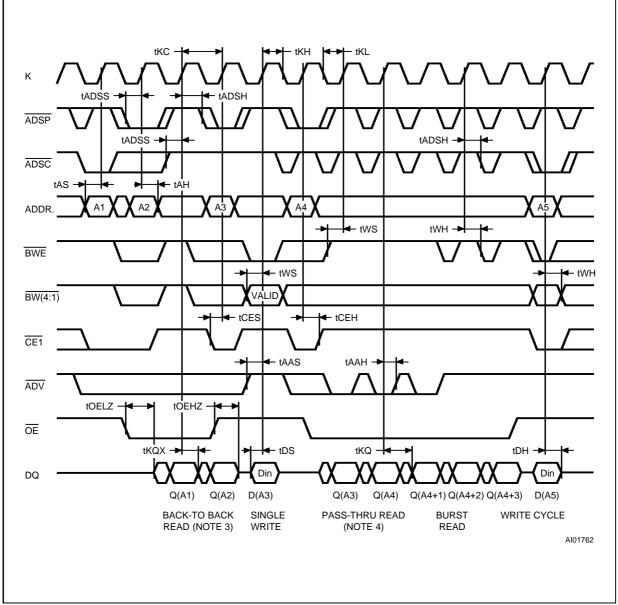

Notes: 1. In this diagram all Chip Enables have identical timing to CE1. CE1 and CE3 are LOW while CE2 is HIGH. CE1 and CE3 are HIGH while CE2 is LOW.

2. GW is HIGH throughout this timing diagram.

3. Back-to-back Read cycles may be controlled by either ADSP or ADSC.

4. Read pass-thru occurs when a Write cycle is followed by a subsequent Read cycle where the previously written data appears at the outputs in the same clock cycle that initiated the Read operation. OE controls the data bus at all times when the device is colored. selected.

Figure 10. 512K Byte Cache Example

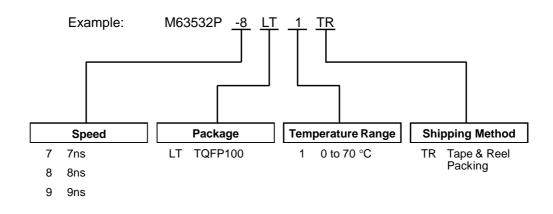

## **ORDERING INFORMATION SCHEME**

For a list of available options (Speed, Package, etc...) refer to the current Memory Shortform catalogue. For further information on any aspect of this device, please contact the SGS-THOMSON Sales Office nearest to you.

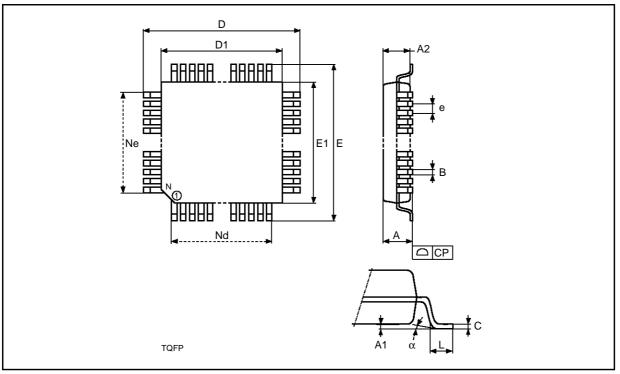

| Symb |      | mm    |            | inches |       |            |  |

|------|------|-------|------------|--------|-------|------------|--|

|      | Тур  | Min   | Max        | Тур    | Min   | Max        |  |

| А    |      | 1.40  | 1.60       |        | 0.055 | 0.063      |  |

| A1   |      | 0.05  | 0.15       |        | 0.002 | 0.006      |  |

| A2   |      | 1.35  | 1.45       |        | 0.053 | 0.057      |  |

| В    |      | 0.22  | 0.38       |        | 0.009 | 0.015      |  |

| С    |      | 0.15  | 0.19       |        | 0.006 | 0.007      |  |

| D    |      | 21.90 | 22.10      |        | 0.862 | 0.870      |  |

| D1   |      | 19.90 | 20.10      |        | 0.783 | 0.791      |  |

| E    |      | 15.90 | 16.10      |        | 0.626 | 0.634      |  |

| E1   |      | 13.90 | 14.10      |        | 0.547 | 0.555      |  |

| е    | 0.65 | _     | -          | 0.026  | _     | -          |  |

| L    |      | 0.45  | 0.75       |        | 0.018 | 0.030      |  |

| α    |      | 0°    | <b>7</b> ° |        | 0°    | <b>7</b> ° |  |

| N    |      | 100   |            |        | 100   | •          |  |

| Nd   |      | 30    |            |        | 30    |            |  |

| Ne   |      | 20    |            |        | 20    |            |  |

| СР   |      |       | 0.10       |        |       | 0.004      |  |

## TQFP100 - 100 lead Plastic Thin Quad Flatpack, 14 x 20mm

TQFP100

Drawing is not to scale

Information furnished is believed to be accurate and reliable. However, SGS-THOMSON Microelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of SGS-THOMSON Microelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. SGS-THOMSON Microelectronics or systems without express written approval of SGS-THOMSON Microelectronics.

© 1996 SGS-THOMSON Microelectronics - All Rights Reserved

® BRAM is a registered trademark of SGS-THOMSON Microelectronics i486 and PENTIUM are trademarks of Intel Corp. Power PC is a trademark of IBM, Corp.

SGS-THOMSON Microelectronics GROUP OF COMPANIES Australia - Brazil - Canada - China - France - Germany - Hong Kong - Italy - Japan - Korea - Malaysia - Malta - Morocco - The Netherlands -Singapore - Spain - Sweden - Switzerland - Taiwan - Thailand - United Kingdom - U.S.A.

20/20